# **N-Channel Enhancement Mode Field Effect Transistor**

### Features

Advanced trench process technology

High-density cell design for ultra low on-resistance

Compact and low profile SOT23 package

#### General Description

This N-Channel enhancement mode power FETs are produced with high cell density, DMOS trench technology, which is especially used to minimize on-state resistance. This device is particularly suited for low voltage application such as portable equipment, power management and other battery powered circuits, and low in-line power dissipation are needed in a very small outline surface mount package. Excellent thermal and electrical capabilities.

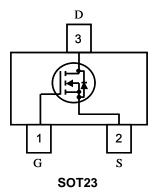

## • Pin Configurations

# Absolute Maximum Ratings @T<sub>A</sub>=25℃ unless otherwise noted

| Parameter                                        |            | Symbol                            | Ratings     | Unit |  |

|--------------------------------------------------|------------|-----------------------------------|-------------|------|--|

| Drain-Source Voltage                             |            | V <sub>DSS</sub>                  | 200         | V    |  |

| Gate-Source Voltage                              |            | V <sub>GSS</sub>                  | ±20         | V    |  |

| Drain Current (1)(2)                             | Continuous |                                   | 2.0         | А    |  |

|                                                  | Pulsed     | l <sub>D</sub>                    | 6           |      |  |

| Power Dissipation                                |            | P <sub>D</sub>                    | 150         | mW   |  |

| Operating and Storage Junction Temperature Range |            | T <sub>J</sub> , T <sub>STG</sub> | -55 to +150 | °C   |  |

# • Electrical Characteristics @T<sub>A</sub>=25°C unless otherwise noted

| Symbol  | Parameter                       | Limit                      | Min                          | Тур | Max  | Unit                                           |  |  |  |

|---------|---------------------------------|----------------------------|------------------------------|-----|------|------------------------------------------------|--|--|--|

| STATIC  |                                 |                            |                              |     |      |                                                |  |  |  |

| VDS     | Drain-Source Breakdown Voltage  | VGS=0V, ID=250μA           | 200                          |     |      | V                                              |  |  |  |

| VGS(th) | Gate Threshold Voltage          | VDS=VGS, ID=250μA          | 1.0                          |     | 3.0  | ٧                                              |  |  |  |

| IGSS    | Gate Leakage Current            | VDS=0V, VGS=±20V           |                              |     | ±100 | nA                                             |  |  |  |

| IDSS    | Zero Gate Voltage Drain Current | VDS=60V, VGS=0V            |                              |     | 1    | μА                                             |  |  |  |

| RDS(ON) | Daria Carras Ca Basistanas      | VGS=10V, ID= 2.0A          |                              | 520 | 580  | - mΩ                                           |  |  |  |

|         | Drain-Source On-Resistancea     | VGS=4.5V, ID= 1.5A         |                              | 650 | 800  |                                                |  |  |  |

| VSD     | Diode Forward Voltage           | IS=1A, VGS=0V              |                              | 0.8 | 1.2  | V                                              |  |  |  |

| DYNAMIC |                                 | ·                          | •                            |     |      | <u>,                                      </u> |  |  |  |

| Qg      | Total Gate Charge               | VDS=30V, VGS=10V, ID=2.0A  | VDS=30V, VGS=10V, ID=2.0A 12 |     |      |                                                |  |  |  |

| Qg      | Total Gate Charge               |                            |                              | 6.5 |      | nC                                             |  |  |  |

| Qgs     | Gate-Source Charge              | VDS=30V, VGS=4.5V, ID=2.0A |                              | 2.2 |      |                                                |  |  |  |

| Qgd     | Gate-Drain Charge               |                            |                              | 2.7 |      |                                                |  |  |  |

| Ciss    | Input capacitance               |                            |                              | 350 |      | pF                                             |  |  |  |

| Coss    | Output Capacitance              | VDS=30V, VGS=0V, f=1.0MHz  |                              | 40  |      |                                                |  |  |  |

| Crss    | Reverse Transfer Capacitance    |                            |                              | 12  |      |                                                |  |  |  |

| Rg      | Gate Resistance                 | VDS=0V, VGS=0V, f=1MHz     |                              | 0.7 |      | Ω                                              |  |  |  |

| td(on)  | Turn-On Delay Time              |                            |                              | 10  |      | ns                                             |  |  |  |

| tr      | Turn-On Rise Time               | VDD=20V, RL =20Ω ID=1A,    |                              | 11  |      |                                                |  |  |  |

| td(off) | Turn-Off Delay Time             | VGEN=10V RG=1Ω             |                              | 29  |      |                                                |  |  |  |

| tf      | Turn-Off Fall Time              |                            |                              | 3   |      |                                                |  |  |  |

### Notes:

(1). Pulse Test : Pulse Width  $< 300 \mu s$ , Duty Cycle < 2%.

(2). Surface Mounted on FR4 Board, t < 10 sec.

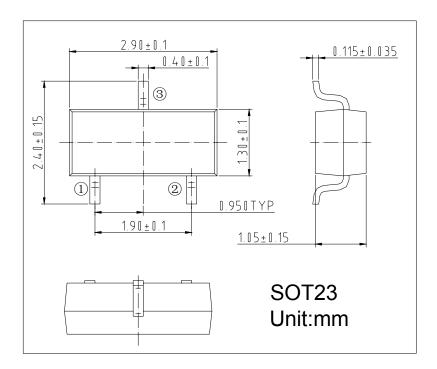

## Package Information

## IMPORTANT NOTICE

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. FORSEMI assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any update. FORSEMI reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.