# 2MHz 2A MAX Output Synchronous Step Down Converter

#### Features

- Soft Start

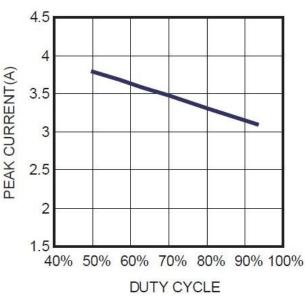

- Internal Current Limit

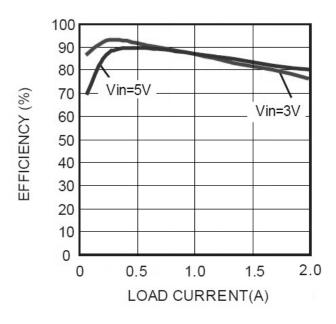

- High Efficiency Up to 95%

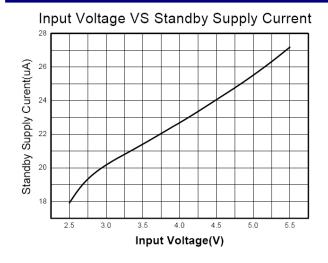

- Very Low Quiescent Current of 40uA

- MAX 2A Output Current at V<sub>IN</sub>=3V

- 2MHz Constant Frequency Operation

- Internal Synchronous Rectifier Eliminates Schottky Diode

- Adjustable Output Voltages From 0.6V to VIN

- Fixed Output Voltage Options Available

- 100% Duty Cycle Low-Dropout Operation

- 0.1uA Shutdown Current

- Tiny SOT23-5L Package

#### Applications

- Blue Tooth Headsets

- Portable Audio Players

- Mobile Phones

- · Wireless and DSL Modems

- Digital Cameras

- Portable Instruments

#### General Description

The FS1405 is a fixed-frequency current-modes Synchronous PWM step down converter that is capable of delivering MAX 2A of output current while achieving peak efficiency of 95%. Under light load conditions, the FS1405 operates in a proprietary pulse skipping mode that consumes just 40uA of supply current, maximizing battery life in portable applications. The FS1405 operates with a fixed frequency of 2MHz, minimizing noise in noise-sensitive applications and allowing the use of small external components. The FS1405 is an ideal solution for applications powered by Li-lon batteries or other portable applications that require small board space.

The FS1405 is available in an adjustable output voltage version capable of generating output voltage version from 0.6V to  $V_{IN}$ . The FS1405 is available in the tiny 6-pin SOT23-5L package.

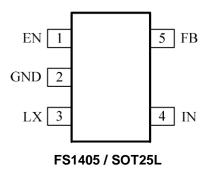

#### Pin Configurations

## Absolute Maximum Ratings

| Parameter                                                                                                                   | Symbol              | Ratings                       | Unit                   |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|------------------------|

| IN Pin Voltage                                                                                                              | V <sub>IN</sub>     | -0.3 to 7V                    | V                      |

| FB Pin Voltage                                                                                                              | $V_{FB}$            | -0.3 to 7V                    | V                      |

| EN Pin Voltage                                                                                                              | V <sub>EN</sub>     | -0.3 to 7V                    | V                      |

| SW Pin Voltage                                                                                                              | V <sub>sw</sub>     | -0.3 to V <sub>IN</sub> + 0.3 | V                      |

| Continuous SW Current                                                                                                       | I <sub>sw</sub>     | Internally limited            | Α                      |

| Maximum Power Dissipation (derate 5.3mW/ $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | P <sub>D</sub>      | 530                           | mW                     |

| Operating Junction Temperature                                                                                              | T <sub>opr</sub>    | -40 to + 150                  |                        |

| Storage Temperature Range                                                                                                   | T <sub>stg</sub>    | -55 to + 150                  | $^{\circ}\!\mathbb{C}$ |

| Lead Temperature (Soldering, 10 seconds)                                                                                    | T <sub>solder</sub> | 300                           |                        |

#### Electrical Characteristics

(  $V_{IN}=V_{EN}=3.6V$ ,  $T_A=25^{\circ}$ C  $C_{in}=4.7Uf$   $C_{out}=10uF$  all capacitors are ceramic, unless otherwise specified.)

| Parameter                             | Symbol            | Conditions                                         | Min   | Тур   | Max   | Units |

|---------------------------------------|-------------------|----------------------------------------------------|-------|-------|-------|-------|

| Input Voltage Range                   | V <sub>IN</sub>   |                                                    | 2.5   |       | 6.5   | V     |

| Under Voltage Lockout Threshold       | V <sub>UVLO</sub> | V <sub>IN</sub> rising, hysteresis =0.1V           | 2.25  | 2.4   | 2.5   | V     |

| Operating Supply Current              |                   | V <sub>FB</sub> =60%,I <sub>OUT</sub> =0           |       | 586   |       | uA    |

| Standby Supply Current                |                   | V <sub>FB</sub> =105%,I <sub>OUT</sub> =0          |       | 33    | 40    | uA    |

| Shutdown Supply Current               |                   | V <sub>EN</sub> =0V,V <sub>IN</sub> =4.2V          |       | 0.1   | 5     | uA    |

|                                       |                   | T <sub>A</sub> =25℃                                | 0.591 | 0.6   | 0.609 | V     |

| Adjustable Version Regulation Voltage | $V_{FB}$          | 0°C <t<sub>A&lt;85°C</t<sub>                       | 0.588 | 0.6   | 0.612 | V     |

|                                       |                   | -40℃ <t<sub>A&lt;85℃</t<sub>                       | 0.582 | 0.6   | 0.618 | V     |

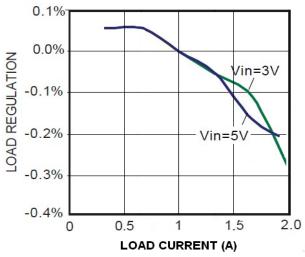

| Output Voltage Line Regulation        |                   | V <sub>IN</sub> =3V to 5V                          |       | 0.016 | 0.4   | %/V   |

| Output Voltage Load Regulation        |                   | I <sub>out</sub> =10mA to 1500mA                   | 1     | 1     |       | %     |

| Inductor Current Limit                | I <sub>LIM</sub>  | $V_{IN}$ =3.0V, $V_{FB}$ =90% of $V_{out(NOM)}$    |       | 2.5   |       | Α     |

| Oscillator Frequency                  | f <sub>SW</sub>   | V <sub>FB</sub> or V <sub>OUT</sub> in regulation  |       | 2     |       | MHz   |

| PMOS On Resistance                    | R <sub>ONP</sub>  | I <sub>SW</sub> =-100mA                            |       | 0.25  |       | Ω     |

| NMOS On Resistance                    | R <sub>ONN</sub>  | I <sub>SW</sub> =100mA                             |       | 0.23  |       | Ω     |

| SW Leakage Current                    |                   | EN=GND,V <sub>IN</sub> =5.5V V <sub>SW</sub> =5.5V |       |       | 1     | uA    |

| EN Logic High Threshold               | V <sub>IH</sub>   | V <sub>IN</sub> =2.7V to 5.5V                      | 1.4   |       |       | V     |

| EN Logic Low Threshold                | V <sub>IL</sub>   | V <sub>IN</sub> =2.7V to 5.5V                      |       |       | 0.4   | V     |

| EN Input Bias Current                 | I <sub>EN</sub>   | V <sub>IN</sub> =5.5V,EN=GND or IN                 |       | 0.01  | 0.1   | uA    |

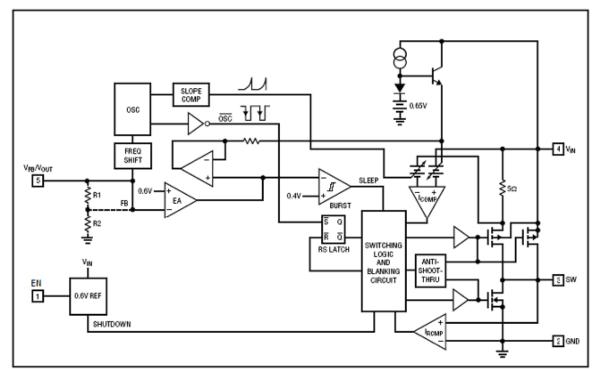

# Typical Block Diagram

## Pin Description

FS1405 - 1234

| DESIGNATOR | SYMBOL                   | DESCRIPTION  |

|------------|--------------------------|--------------|

| 12         | Output Detection Voltage | AD=ADJ       |

| 34         | Package Type:            | SK: SOT23-5L |

| NO: | Pin Name | Pin Description                                                                                    |

|-----|----------|----------------------------------------------------------------------------------------------------|

|     | - FN     | Enable Control Input. Drive EN to IN or to a logic high for normal operation, drive to GND or a    |

| (1) | EN       | logic low to disable the regulator.                                                                |

| 2   | GND      | Ground.                                                                                            |

| 3   | LX       | Switching Node Output. Connect this pin to the switching end of the inductor.                      |

| 4   | IN       | Power Input. Bypass to GND as close as possible to the IC with a high quality ceramic capacitor.   |

|     |          | Feedback Node. For fixed output voltage options, connects this pin directly to the output. For the |

| (5) | FB       | Adjustable output version the voltage at this pin is regulated to 0.6V; connect to this pin to the |

|     |          | center of the output voltage feedback network.                                                     |

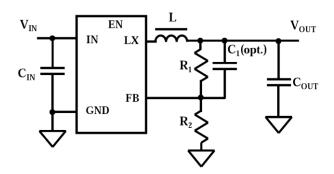

#### • Application Information

#### **Application note:**

1. Inductor Value (Table 1)

**Table 1. Typical Inductor Values**

| V <sub>out</sub> | 0.6V to 0.9V | 0.9V to 1.8V | >1.8V |

|------------------|--------------|--------------|-------|

| L                | 1.5uH        | 2.2uH        | 2.7uH |

- 2,  $C_{in}$ =4.7uF(ceramic capacitor).

- 3. Cout=10uF(ceramic capacitor).

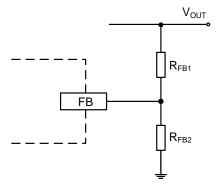

- 4. Output Voltage Programming

Figure 1. Output Voltage Programming

Figure 1 shows the Feedback network necessary to set the output voltage when the adjustable version is used. Select the proper ratio of the two feedback resistors  $R_{_{FB1}}$  and  $R_{_{FB2}}$  based on the desired output voltage. Typically choose  $R_{_{FB2}} \approx 100 K \Omega$  and determine  $R_{_{FB1}}$  from the output voltage:

$$R_{FB1} = R_{FB2} (\frac{V_{OUT}}{0.6V} - 1)$$

Connect a small capacitor across  $R_{\mbox{\tiny FB1}}$  for feed forward capacitance at the FB pin:

$$C_{ff} = 2 \times 10^{-5} / R_{FB1}$$

where  $R_{\text{\tiny FB1}}$ =900K  $\Omega$  use 22pF. When using very low ESR output capacitors, such as ceramic, check for stability while examining load-transient response, and increase the compensation capacitor  $C_1$  if needed.

#### 5. Dropout Operation

As the input supply voltage decreases to a value approaching the output voltage, the duty cycle increases toward the maximum on-time. Further reduction of the supply voltage forces the main switch to remain on for move than one cycle until it reaches 100% duty cycle. Possible occurred larger ripple on the low-dropout operation. Recommended operating voltage  $V_{\text{\tiny IN}} \geqslant V_{\text{\tiny OUT}} + 0.7V$

#### **PCB** layout caution

- 1. The power traces, consisting of the GND trace, the SW trace and the Vin trace should be keep short, direct and wide.

- $2 \cdot V_{fb}$  should be connected directly to the feedback resistors, The resistive divider R1/R2 must connected between the (+) plate of  $C_{out}$  and ground.

- 3. The (+) plate of Cin should be connected to Vin as closely as possible, because this capacitor provides the AC current to the internal power MOSFETS.

- 4. Keep the switching node SW away form the sensitive  $V_{fb}$  node

- 5. Keep the (-) plates of C<sub>in</sub> and C<sub>out</sub> as close as possible

- 6. The high current paths

- 7. The recommended PCB layout

#### Typical Performance Characteristics

For FS1405

# FS1405

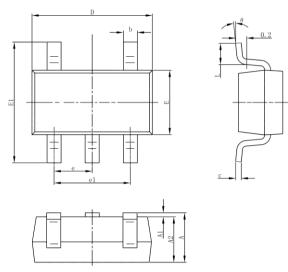

# Package Information

#### SOT-23-5L PACKAGE OUTLINE DIMENSIONS

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min          | Max           | Min                  | Max   |  |

| Α      | 1.050        | 1.250         | 0.041                | 0.049 |  |

| A1     | 0.000        | 0.100         | 0.000                | 0.004 |  |

| A2     | 1.050        | 1.150         | 0.041                | 0.045 |  |

| b      | 0.300        | 0.500         | 0.012                | 0.020 |  |

| С      | 0.100        | 0.200         | 0.004                | 0.008 |  |

| D      | 2.820        | 3.020         | 0.111                | 0.119 |  |

| Е      | 1.500        | 1.700         | 0.059                | 0.067 |  |

| E1     | 2.650        | 2.950         | 0.104                | 0.116 |  |

| е      | 0.950(BSC)   |               | 0.037(E              | BSC)  |  |

| e1     | 1.800        | 2.000         | 0.071                | 0.079 |  |

| L      | 0.300        | 0.600         | 0.012                | 0.024 |  |

| θ      | 0°           | 8°            | 0°                   | 8°    |  |